ハードウェア仕様

以下、特に指定がなければ、ATmega168版(TGmega)、ADuC7026版(TG7026)、 V850版(TGV850)に共通の仕様です。

また、特に指定がなければ、2007/06/26 版(V 1.01) のソフトウェアに対応する説明です。

●ハードウェア (ADuC7026版)

まず、CQ 出版「デザインウェーブマガジン」2006年3月号付録基板(FRK-ADuC) 自体に、

デカップリング(バイパス)・コンデンサの不足で動作が不安定という欠点がありますから、

コンデンサを追加して、基板自体が安定して動くようにする必要があります。

まず、CQ 出版「デザインウェーブマガジン」2006年3月号付録基板(FRK-ADuC) 自体に、

デカップリング(バイパス)・コンデンサの不足で動作が不安定という欠点がありますから、

コンデンサを追加して、基板自体が安定して動くようにする必要があります。

問題を完全に解決するには、「足上げ」とか、 チップをいったん剥がしてパターンを修正するなどの対策が必要で、 それなりの設備やスキルが要求されます。

最も簡単な対策としては、基板裏面の、チップの真裏あたりのGND/VDDパターンの レジストを剥がして、数μFのチップ積層セラミック・コンデンサを ハンダ付けすることです。私もそうしています。

また、シリアル MIDI の場合には CN5 の DSUB-9P 端子からの信号を使いますので、 コネクタの実装が必要です。 ごく普通の「IBM-PC用9ピン・シリアルケーブル」を使うなら、DSUB-9P メス・コネクタを 基板の裏面側に付ける必要があります。

ジェンダー・チェンジャーなどを使用して、 基板にオス・コネクタを付ける場合には基板の表面側に付けます。 シリアル経由でフラッシュの書き込みをしているなら、すでに実装ずみのはずです。

ADuC7026には内蔵RCクロックがありますが、一応「楽器」なので、周波数精度の点で、 外付けの 32.768 kHz クリスタルが必要です。 プログラムは外付けクリスタルの使用を前提としていますから、 内部クロックを使うように変更してコンパイルし直さない限り、 クリスタルを付けずに正常に動作させることはできません。

最小構成としては、以上の準備のもとに、CN2-B10 (DACout3) から オーディオ出力 (max 2.5 Vp-p) を取り出すだけです。 エイリアス除去用の LPF もあれば望ましいのですが、 PWM 出力と違って必須ではありません。 拡張用基板に接続せずに、FRK-ADuC スタンドアロンで使えます。 LCD がないので表示は見えませんが、 SW2 (リセットスイッチでない方)の操作は「INC ボタン」として有効です。

最大構成(→回路図 )としては、 拡張用基板に LCD、タクトスイッチ、ロータリー・エンコーダー、 CPU ロードメータ用の RC などを実装します。

ところで、私は FRK-ADuC 基板を2枚持っているのですが、 実は、このふたつでプログラムの実行速度が違うのです。 つまり、「遅いチップ」と「速いチップ」があるようなのです。 「遅いチップ」のリビジョンは「H3T」、「速いチップ」のリビジョンは「I30」です。

プログラムの開発は、ずっと「H3T」の方で行っており、ある程度完成したところで、 もうひとつの基板で試してみたところ、スピードの違いに気が付きました。 これが、本当にチップリビジョンの違いによるものか、それとも、 いろいろやっているうちに、どこか少し壊してしまったせいなのか、わかりません。

チップのバグ情報である「Silicon Anomaly List」は、リビジョン「I30」に対するものは 見つかりましたが、肝心の「H3T」に関するものは見つかりませんでした。 そのため詳細はわからないのですが、「I30」の「Silicon Anomaly List」に 気になる記述があります。

パフォーマンス関係に、参照番号「pr003」の「Execution speed」というのがあり、 解決済み(fixed)となっています。もしこれが、「H3T」では解決されておらず、 「I30」で解決されたのなら、実行スピードに差があることが納得できます。

ともかく、速度が違う両方のボードで CPU 能力をフルに使うために、 初期化ルーチン内で CPU 速度を測定して、遅いチップでは低いサンプリング周波数を、 速いチップでは高いサンプリング周波数のコンフィギュレーションを選択しています。

| 同時発音数 | 1 | 2 | 3 | 4 | 5 |

|---|---|---|---|---|---|

| サンプリング周波数 | 44 kHz | 29 kHz | 21 kHz | 17 kHz | 13 kHz |

| CPU 負荷 | 84 % | 86 % | 87 % | 90 % | 85 % |

| 同時発音数 | 1 | 2 | 3 | 4 | 5 |

|---|---|---|---|---|---|

| サンプリング周波数 | 28 kHz | 19 kHz | 15 kHz | 11 kHz | 8 kHz |

| CPU 負荷 | 80 % | 86 % | 95 % | 90 % | 81 % |

●ハードウェア (ATmega168版)

使用する AVR としては ATmega168 が必要です。

16 Kバイトのプログラム領域を、ほぼ 100 % 使用しています。

機能を絞ってプログラム量を削減すれば ATmega88 に入るかも知れません。

しかし、ATmega48 には無理でしょう。

使用する AVR としては ATmega168 が必要です。

16 Kバイトのプログラム領域を、ほぼ 100 % 使用しています。

機能を絞ってプログラム量を削減すれば ATmega88 に入るかも知れません。

しかし、ATmega48 には無理でしょう。

最小構成(→回路図)としては、 普通に ATmega168 が動作する環境 + MIDI 入力インターフェース+PWM用LPFとなります。 もし、ターゲットのボード上でフラッシュ書き込みをしないならば、ISP コネクタは 必要ありません。

PWM用LPF を LC フィルタで構成し、シリアルMIDIインターフェースに「9-KE」ケーブルを使えば、 ハンダ付けして基板を作らなくても、ブレッド・ボード上で試せると思います。

最大構成(→回路図 )では、基板上に LCD、タクト (プッシュ)・スイッチ、ロータリー・エンコーダー、PWM用LPF、 ディジタル・オーディオ用 DAC (ROHM BU9480F)、CPU ロードメーター用 RC などを実装します。

電源は +5V とし、クロックは 24 MHz を使います。 これは、スペックの規定を超えています。それでは気持ち悪いという方のために、 スペックに合った 20 MHz クロック・バージョンのオブジェクトも用意してあります。

すべてのタイミングは、CPU クロックを分周して生成しているので、 クロック周波数が変わっても、結果であるサンプリング周波数が変わるだけです。 決して、CPU 負荷がクロックに応じて大きくなったり小さくなったりするわけではありません。

オブジェクトとしては用意してありませんが、ソースプログラム中では上記以外に、 18.432 MHz、19.6608 MHz、 24.576 MHz のクロック周波数に対応できるようになっています。

24 MHz クロックを使った理由は、フラッシュ書き込みに オプティマイズ社の「MINI EZ-USB」を使用したため、 USBのタイミングとして使われる 24 MHz クロック出力が利用できたからです。

当初はこの 24 MHz 外部クロックを利用していましたが、クロック周波数変更のテストのため、 後から外付けクリスタルに変更しました。 「MINI EZ-USB」からは、このほかに、USB 経由の +5V 電源も AVR 側に供給しています。

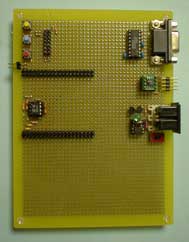

回路図には 6 ピンの ISP コネクタを書いてありますが、実際には、

左の基板の写真にある通り、6 ピンコネクタは実装せず、「MINI EZ-USB」からの信号を

直接接続してあります。

回路図には 6 ピンの ISP コネクタを書いてありますが、実際には、

左の基板の写真にある通り、6 ピンコネクタは実装せず、「MINI EZ-USB」からの信号を

直接接続してあります。

また、「MINI EZ-USB」をAVR書込み器として動作させるための プログラム「spi.iic」を書き込んだ I2C EEPROM (24LC64)を実装してあります。 これは「TGmega」プログラムとは関係ありません。

「MINI EZ-USB」による AVR 書込みについては、ここでは説明しませんので、 興味ある方は、オプティマイズの Web ページを参照してください。

ヒューズ・ビットに関しては、クリスタルを接続するか、外部オシレータを接続するかに 応じて適切に設定してください。 内部クロックではスピードが足りません。 プログラム中でシステムクロック・プリスケーラの操作はしていないので、 あらかじめフューズビットで 8分周は「なし」に設定しておきます。 具体的には、お使いになる書込み器の操作方法にしたがって設定してください。

ちなみに、オシレータからコンデンサを介してAC結合で「XTAL1」ピンに クロック入力してやれば、外部クリスタル使用の設定で外部オシレータを使って 動作させることができます。 (もちろん XTAL2 ピンは発振回路に使われてしまいます)

また、クリスタルの代わりにセラミック振動子(セラロック)を使うことができますが、 セラミック振動子の場合、周波数偏差が大きくてピッチが狂った状態になる可能性があります。 ATmega版の場合、周波数テーブルは半音を 16 分割した、 つまり 100 / 16 = 6.25 セント置きのピッチしか発生できないので、 ファインチューニングでもこの間隔でしか設定できません。

これが問題になる場合には、周波数テーブルをセラミック振動子の 実際の周波数に合わせて作り直す必要があります。 逆に言えば、周波数テーブルの作り直しを覚悟すればセラミック振動子で 構わないことになります。

MIDI 音源としての同時発音数は2ですが、 サンプリング周波数を下げて同時発音数を増やせるかというと、 ATmega168 では内蔵 RAM 容量が少なくて難しいと思います。 クロック周波数は 16 MHz と低いけれど、 内蔵 RAM 容量の大きい ATmega128 などに移植すれば同時発音数は増やせるかも知れません。

| クロック 周波数 |

24.576 MHz | 24.000 MHz | 20.000 MHz | 19.6608 MHz | 18.432 MHz |

|---|---|---|---|---|---|

| サンプリング周波数 | 16.000 kHz | 15.625 kHz | 13.020 kHz | 12.800 kHz | 12.000 kHz |

| 31.25 kbps 誤差 | +0.3 % | 0 % | 0 % | +0.83 % | -0.37 % |

| 38.4 kbps 誤差 | 0 % | +0.6 % | -1.36 % | 0 % | 0 % |

●ハードウェア(V850版)

CQ出版「インターフェース」2007年5月号付録基板(CQ_V850)では、 クロック発振にセラロックを使用しています。セラミック振動子は、 水晶に比べると、初期周波数偏差が大きい、安定度が低いといった傾向があります。 残念ながら、私の持っている基板では、+0.24 % 程度の周波数偏差がありました。 音程にして約 4 セントのずれです。

左の写真が最小構成で、シリアルMIDI入力と 8 ビットDAC出力だけをサポートしています。 外部基板は使用せず、付録基板の部品面のコネクタ部に直接、部品を実装しています。 その関係で、回路図では Top View でコネクタを書いてあります。 (→回路図)

2007/05/18 版 (V1.00) のソフトウェアでは「暫定版」として、 LCD/キー入力に対応していませんでした。 2007/06/26 版 (V1.01) のソフトウェアで LCD/キー入力をサポートしましたが、 この版では、LCD/キー入力を使うか使わないかに関わらず、 プルアップ抵抗(R103 〜 R106 の4本)が必要です。

ADuC7026 および ATmega168 では、チップの機能としてプルアップ抵抗が内蔵されているので、 それを利用していますが、V850 では内蔵プルアップ抵抗がないので、外部でプルアップする必要が あります。

V850 では一部のポートでは、3.3V CMOS レベル入出力のほかに、 5V トレラント入力かつ Nch オープンドレイン出力に設定できます。 その場合、3.3 V へのプルアップは有用ではないので、 使うんだったら外部で +5V にプルアップしてね、ということなのでしょう。

上の写真は「暫定版」のもので、プルアップ抵抗がついていません。

8 ビットDAC出力は負荷電流が取れないので、Nチャネル J-FET(2SK30A) のソースフォロアで バッファしてあります。(写真では USB コネクタの下)

写真では、JTAG コネクタ位置にシリアル MIDI 入力を接続しているのが見えていると思いますが、 これは単にピンヘッダを立てるスペースとして利用しているだけで、 JTAG 信号は全く利用していません。

シリアルMIDI入力は「9-KE」ケーブルを使用していますが、 ケーブルの出力はオープンコレクタなので、プルアップ抵抗が必要です。

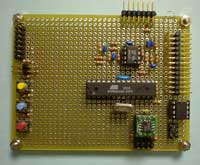

左の写真が最大構成版です。 外部 16 ビット DAC として ROHM BU9480F を使用しています。 LCD、タクトスイッチ、ロータリーエンコーダーを実装しています。 8 ビット DAC 出力は OP アンプでバッファしています。 (→回路図)

基板の下半分が大きく空いているのは、空きスペースに CQ_V850 基板をもう一つ実装して、単純に並列動作 させることにより、同時発音数を倍にすることを考えているからです。

回路図では、MIDI インターフェース回路自体は示してありませんが、 この回路図の (d) の RS232C インターフェース IC を 使ったシリアル MIDI 回路と、(e) の 4 ピン汎用フォトカプラを使った MIDI 入力回路を 実装してあります。

バッファの OP アンプは LM358 を +5V 単電源で使用しています。 8 ビット DAC 出力は 3.3Vp-p で、そのままだと 5V 電源時の LM358 の 入力電圧範囲を超えてしまいます。

ここでは、性能を求めていないので、簡単に入力側で抵抗分圧して 2.5Vp-p 程度にしています。 モダンな、レイル・ツー・レイル入力の OP アンプを使う場合は、 入力に DAC 出力を直結でいいと思います。

RS232C とトランシーバ IC OP アンプは LCD / V850 基板の下に実装してあるので、 LCD / V850 基板をはずした写真を左に示します。

V850 のマニュアルでは、8 ビット DAC の負荷インピーダンスが 2 MΩ 以上であることを 求めているので、分圧抵抗を高抵抗にしました。 OP アンプ入力のバイアス電流の影響が無視できませんが、性能を求めていないので、 気にしないことにします。

付録基板では、USB-シリアル変換 IC を介して、PC と V850 の UARTA0 とが つながるようになっています。 デバッガ ID850QB-MON は UARTA0 を専有して機能を実現しているので、 デバッガの利用を前提にするなら、ユーザプログラム中では UARTA0 の使用はできません。

V850 版は ADuC版の移植版ですから、ソースレベルデバッギングは、 ないと困るという機能ではありません。 しかし、デバッガを利用すれば、付録基板上のジャンパを抜き差しせずに、 PC上の操作だけでプログラムの実行 / 停止 / フラッシュ書込みが実現できるので 開発の効率が上がります。

そういうわけで、MIDI 入出力としては UARTA2 を利用し、UARTA0 はデバッガに 開放することとしました。

もうひとつの理由としては、PCのシリアル MIDI ドライバでは、 本物の COM ポートでしか動作しないものが多く、 仮想 COM ポートで動作するものが少ないことがあげられます。

徹底的に調べたわけではないので、正確なことはわかりませんが、ざっと、 YAMAHA / Roland / KAWAI / KORG の Windows 2000 用シリアル MIDI ドライバのうち、 USB-シリアルで正常動作したのはコルグの「KORG PC I/F MIDI Driver for Windows NT」 だけでした。

この場合でも、コルグのドライバでは、COM1 から COM4 までしかサポートしていないので、 USB-シリアルの仮想 COM ポート番号を COM1 から COM4 の範囲に設定できないと使用不可です。

CQ 基板上の変換チップ CP2102 でも、コルグ・ドライバで MIDI データが流れてくることは、 オシロスコープでシリアル信号を見て確かめてあります。

| 同時発音数 | 1 | 2 | 4 | 6 | 8 |

|---|---|---|---|---|---|

| サンプリング周波数 | 56 kHz | 39 kHz | 23 kHz | 16 kHz | 12 kHz |

| CPU 負荷 | 85 % | 89 % | 87 % | 85 % | 85 % |

●MIDI入力

通常のMIDI入力(31.25 kbps)と、いわゆるシリアルMIDI(38.4 kbps)に対応しています。 ADuC版では基板上のRS232Cインターフェースを使いますので、 シリアルMIDIの場合は外部回路は不要です。 シリアルMIDIは、マルチポートには対応していません。 ポート指定は、単に無視します。

通常のMIDI、つまり電気的にはカレントループを使用し、機構的には DIN-5P コネクタを 使ったインターフェースに対しては、すべての版で外部回路が必要です。

もし、昔のサウンドブラスターのジョイスティックポートに接続する「MIDIケーブル」をお持ちなら、

そのケーブルと結線するだけでMIDI入力が使えます。(左の写真)

もし、昔のサウンドブラスターのジョイスティックポートに接続する「MIDIケーブル」をお持ちなら、

そのケーブルと結線するだけでMIDI入力が使えます。(左の写真)

当時、「MIDIケーブル」は 1,500 円程度のものでしたが、現在となっては、 販売店の店頭で Creative 製の新品を入手することは、ほとんど不可能でしょう。 YAMAHA 製と M-AUDIO 製のケーブルは、現在でも 3,000 円前後で販売されているようです。

PC に接続する D-SUB 15P コネクタのカバー部分に電子回路が組み込まれていて、 1.5 m ほどのケーブルの先に MIDI 機器に接続するための DIN-5P プラグが付いています。 まさに「MIDI ケーブル」です。

一方、右の写真は、Advanced Gravis 社のボックス型の MIDI アダプタで、

通常の MIDI 機器と同様に、メス型の DIN-5P コネクタになっています。

一方、右の写真は、Advanced Gravis 社のボックス型の MIDI アダプタで、

通常の MIDI 機器と同様に、メス型の DIN-5P コネクタになっています。

MIDI IN / OUT / THRU 端子があって、IN、OUT それぞれ、データによって LED が点滅します。

「MIDIケーブル」がない場合は、フォトカプラを使ってインターフェース回路を 自作する必要があります。 フォトカプラは「PC900V」などのディジタル出力型を使用するのが簡単です。 汎用のフォトカプラを使用した結果はこちらにまとめてあります。

ATmega版/V850版でシリアルMIDIを使用する場合は、 RS232Cインターフェース回路を組む必要がありますが、 携帯電話とPCとの接続ケーブル「9-KE」を利用すると、ケーブルへの結線だけですみます。 ケーブルの出力側はオープンコレクタなのでプルアップ抵抗が必要ですが、 ATmega版では内蔵プルアップを利用しているので、外部に抵抗を付ける必要はありません。

「9-KE」の携帯電話コネクタ側を切断して配線しますが、 線の色が回路図に示してあるものと一致するとは限りません。 検索すると「9-KE」の内部回路を解析結果を示している web ページが見つかります。 その回路図を参照してもらえば分かりますが、PC側 からの出力回路は オープンコレクタになっており、PC 側への入力回路は、 RS232C の信号線の電圧を分圧してトランジスタをバイアスする回路になっています。

テスタで導通を調べれば、GND 線 2 本がどれかは、すぐ分かります。 ケーブルを PC につないだ状態で、残り2 本の、 GNDに対する電圧をテスタで測れば、 入力側は 0.数 V、出力側は 0 V となることで判別できます。 ここで、テスタの入力インピーダンスが高いと、オープンコレクタの場合でもノイズが乗って、 いくらかの電圧が出てくるかも知れません。 100 kΩ 程度の抵抗でプルダウンしておいて測定すると良いと思います。

ケーブルへの結線、MIDIインターフェース回路、RS232Cインターフェース回路は、 この 回路図にまとめてあります。 この中で「SENS」という信号が、接続されるインターフェースの種類を判別するためのもので、 CPU 側はリセット後の各種イニシャライズ時に、この信号の状態をセンスし、 オープンであれば「シリアル MIDI」、グランドに接続されていれば「通常の MIDI」と判断します。

判断の結果は、LCD に最初に表示されるバナー・メッセージ中に示されます。 通常の MIDI であれば「MIDI」と表示される部分が、 シリアル MIDI の場合は「S-MIDI」という表示になります。

● MIDI出力

基本的には、MIDI出力は全く使用していませんが、 プログラムの変数「midi_thru」の初期値を 1 に変更してコンパイルし直すと、 アクティブ・センシング以外の MIDI メッセージ入力が、 すべて MIDI 出力にスルーされるようになります。

● PWM による DA 出力用 LPF (TGmega版)

ATmega には DA コンバータは内蔵されていないので、外付け DAC を使用しない場合には、 タイマ1の PWM 機能を利用してアナログ出力を実現します。 ここでは、9 ビット PWM モードを選択しました。 したがって、CPU クロックの 24 MHz を 512 分周した 46.875 kHz が PWM 周波数となります。

サンプリング周波数は PWM 周波数の整数分の1であると都合が良いので、 1/3 の 15.625 kHz としました。 アンチ・エイリアス・フィルタとしては、約 8 kHz 以上を減衰させれば良いことになります。

PC のオーディオ・インターフェースを利用して録音することを考えると、 アンチ・エイリアスのためのフィルタリングは、PC に取り込んだ後に 波形編集ソフトウェア上で実行できますから、 必ずしも実際のハードウェアで実装する必要はありません。 一方、PWM 周波数の減衰が十分でないと、録音時のサンプリング周波数との ビート(差周波数)が、肝心のオーディオ帯域に飛び込む可能性があります。

そういったわけで、LPF としては、カットオフ周波数 fc = 8 kHz の 3次バタワース・フィルタを選びました。 LC によるパッシブ・フィルタと、Sallen-Key 回路によるアクティブ・フィルタの 2種類の方法で実現しました。(→回路図) 出力の直流カット用のコンデンサは省略してあります。

パッシブ・フィルタには、必ず信号が減衰するという弱点がありますが、 オーディオ信号用としては、かえって好都合で、 さらに減衰させて -14 dB 程度のゲインとしています。 これで 5Vp-p の PWM 波が 1Vp-p 程度のアナログ波になります。 アクティブ・フィルタの場合でも同様です。

フィルタの設計といえば、通常、表を引いたり、設計ソフトウェアを利用しますが、 3次バタワース π 型 LC LPF の場合、 規格化素子値(角周波数 1 rad/s、入出力インピーダンス 1 Ωに対する素子値)は R = 1、C = 1、L = 2 ですから、表を引くまでもなく、 何の苦もなく記憶しておくことができます。 あとは、周波数スケーリング、インピーダンス・スケーリングを 電卓で計算するだけで設計が完了します。

アクティブ・フィルタの Sallen-Key 回路は、通常、2次のものが使われますが、

入力側に一次 RC フィルタを追加して、3次のフィルタとして使うこともできます。

ただし、定数の計算は面倒なので、設計ソフトウェアを利用することになります。

こちらのサイト

「The Art of Analog Circuits」で

3次 Sallen-Key フィルタの設計用 Excel シートが公開されています。

アクティブ・フィルタの Sallen-Key 回路は、通常、2次のものが使われますが、

入力側に一次 RC フィルタを追加して、3次のフィルタとして使うこともできます。

ただし、定数の計算は面倒なので、設計ソフトウェアを利用することになります。

こちらのサイト

「The Art of Analog Circuits」で

3次 Sallen-Key フィルタの設計用 Excel シートが公開されています。

このシートを使って設計するためには、「Low-Pass」のシートに フィルタの伝達関数(の分母)の多項式の係数を与える必要がありますが、 3次バタワースの場合は a = 1、b = 1、c = 1 を入れれば良く、 これも何の苦もなく記憶しておけます。

「Low-Pass」シートのセル L4, L5, L6 を1にし、L7 から L13 までをブランクにして 「Go」ボタンを押すと、B7 から B13 に、キャパシタを同一値に揃えた 規格化素子値が表示されます。 セル X6, X7 にそれぞれ実際の周波数、R1 の抵抗値を入れれば、 実際の素子値が L8 から L12 に表示されます。

計算上オペアンプのゲイン K = 1.985・・・ となりますが、ここでは精度を求めていないので、 簡単のため、K = 2 とします。 同様に RC の値も E24 系列に存在する値で 近似して、R1 = R2 = 3 k、R3 = 820、C1 = C2 = C3 = 10 nF としました。

オペアンプ用の電源は特に用意せず、ロジック用の +5V 単電源で動作させます。 オペアンプの単電源動作で問題になるのが入出力電圧範囲です。 最近の製品では入力レイル・ツー・レイル、出力フルスイングの品種がありますが、 少し前の製品でも使えるように、入出力電圧範囲を GND から 3V 程度までに 制限することにしました。

オーディオ用としては、トータルで減衰していたほうが都合が良いので、 オペアンプ部のゲイン K = 2 を考慮し、入力部で約 1/10 (-20 dB) にしています。 さらに、出力が 2.5V 程度を中心に振るように、 入力部で +5V に吊って DC オフセットを加えています。(図(a) の R803) CV/エンベロープ用では DC オフセットは不要なので +5V に吊っていません。

オペアンプのゲインを決めている抵抗(図(a)の R806, R807)は LM358/LM2904/LM324/LM2902 の 出力段のバイアス電流を流す抵抗を兼ねています。 出力からのシンク電流 0.5 mA 程度まではクロスオーバー歪は発生しません。 もし、負荷インピーダンスが低くて、電流がもっと必要なら、R806, R807 の値を 小さくしてください。

上の写真の製作例では、コンデンサに積層セラミック(青い部品)を使っていますが、信号用としては性能が 十分ではないので、性能を重視する方はフィルム・コンデンサを使ってください。

タイマ 1 の OC1B 出力は、現在、パート 0 のオペレータ 1 (キャリア)の エンベロープの値を出力するようになっています。 主な目的は、オシロスコープで EG 波形を観察して EG プログラムをデバッグするためです。

● ディジタル・オーディオ用DAC (ROHM 製 BU9480F) (ATmega版と V850版)

多ビット精度の外付けDACを、ピン数の少ないマイコンで利用する場合、 当然パラレル接続は無理で、シリアル接続をする必要があります。 通常、シリアル接続の規格として、SPI(Serial Peripheral Interface)や、 I2C(Inter Integrated Circuit)がインターフェースを持つものが使われます。

ROHM のローエンド・ディジタル・オーディオ用 DAC BU9480F」 (16 ビット、 ステレオ、1.27 mm ピッチ 8 ピン SOP パッケージ)が鈴商で 安価(単価 210 円)で販売されていたので、AVR および V850 への接続を試み、うまく行きました。 その詳細の説明については作成中です。

2.54 mm ピッチのユニバーサル基板上で製作するために、 8ピン SOP->8ピンDIP変換基板(100 円 / 9 = 11 円、秋月扱い)、 8 p 連結ピン(100 円、秋月扱い)を使用しました。

AVR システムのリソースとしては、タイマ 0、タイマ 2、SPI を使用します。 PWM による DA と同時に出力させると、割り込み処理が重くなるので、 MIDI 入力の切り換えのように、DAC センス入力を設け、選択されていない側の処理を 省いています。

DAC センス入力が GND に落ちていれば DAC が接続されていると判断し、 タイマ 0, 2 / SPI をセットアップし、ディジタル・オーディオ DAC 側に出力します。

このとき、タイマ 1 の PWM はセットアップされますが、割り込みは発生せず、 オーディオ出力としては使われません。エンベロープ出力は割り込みを使っていないので 影響ありません。

V850 では、3線式可変長シリアル I/O (CSIB) で 16 ビットシリアルデータの送信ができるので、 これを利用して、ディジタル・オーディオ DAC に出力しています。

一般的なオーバーサンプリング・ディジタル・オーディオ DAC に 必要とされる 256fs や 384fs の クロックを生成していないので、BU9480F 専用になっています。 処理を少し手抜きして負荷を軽くしてあるので、ATmega 版とは違って、 常に 8 ビット DAC 出力と 16 ビット DAC 出力とを両立させています。

ADuC7026 は内蔵 12 ビット DAC があるので、ディジタル・オーディオ DAC を接続していません。 もともと、12 ビット精度に見合ったエントリ数のサイン波テーブルを使っていますから、 16 ビット DAC を接続したからと言って、それだけで音質が良くなるわけではありません。

● LCDと入力キー

16 文字 X 2 行のキャラクタ LCD を接続して、各種の表示をすることができます。

また、タクト(プッシュ)スイッチあるいは(インクリメンタル)ロータリー・エンコーダを

接続して、各種の操作をすることができます。

→操作方法

16 文字 X 2 行のキャラクタ LCD を接続して、各種の表示をすることができます。

また、タクト(プッシュ)スイッチあるいは(インクリメンタル)ロータリー・エンコーダを

接続して、各種の操作をすることができます。

→操作方法

LCD としては、 HD44780 互換のコントローラを使用したタイプを想定しています。 といっても、HD44780 はデファクト・スタンダードになっているので、 互換でないキャラクタ LCD モジュールを探すほうが難しいです。

表示レイアウトは 16 文字 X 2 行を基準にしていますが、 20 文字 X 2 行のタイプでも右の 4 カラム分がブランクになるだけで、表示は可能です。 これは、手持ちの LCD モジュールで確かめてあります。

20 文字 X 4 行のタイプでは、左上の 16 文字 X 2 行分だけが表示される形になりますが、使用はできるはずです。 これは、手持ちがないので、確認はしていません。

マイコンとのインターフェースは 4 ビットモードで行っています。 R/W 端子は L 固定で、LCD へは出力オンリーです。 さらに、マイコン側の必要ピン数を減らすために、ひとつのポートに LCD 出力と SW 入力の ふたつの機能を持たせています。

LCD の「E」信号が「H」の期間は、ポートを出力モードにして LCD へデータを出力し、 「E」信号が「L」の期間はポートを入力モードにして、スイッチの状態を読み取ります。

もちろん、スイッチと出力ポートを直結すると互いに「衝突」して過電流が 流れるおそれがあります。 そのため、各スイッチは直列抵抗の 10 kΩ を介して GND に落とすようになっています。 また、回路図には表れていませんが、マイコン・チップ内部の プルアップ抵抗と LCD モジュール内部のプルアップ抵抗が存在しています。

形式的な言い方をすれば、「弱い抵抗性の1」であるプルアップ抵抗と、 OFF 状態では「ハイインピーダンス」、ON 状態では「強い抵抗性の0」であるスイッチとを 接続すると、スイッチが OFF では「弱い抵抗性の1」、ON では「強い抵抗性の0」となります。

これが入力モードのマイコンのポートに接続されていれば、マイコン側は「ハイインピーダンス」 なので、スイッチ側の論理レベルが勝って、スイッチの状態に応じたレベルが 入力されることになります。

マイコンのポートが出力モードの時は、「駆動性」の論理強度ですから、 「抵抗性」のスイッチ側の値は負けて、出力ポートの値が、そのまま LCD モジュールに 入力されることになります。

この形式的な話が、実際に成り立つためには、スイッチに直列に入れる抵抗値の選び方が 問題になります。 マイコン内部のプルアップと LCD モジュールのプルアップとの並列抵抗値は、 大体 20 kΩ ∼ 30 kΩ 程度と思われます。 これを GND 側に引っ張って、確実に「0」レベルとするためには、 直列抵抗はプルアップ抵抗値より小さい値を選ぶ必要があります。

一方、小さすぎると、出力モードのポートに無駄な電流を流すことになります。 回路図の 10 kΩ という値は、そういう根拠で選んだもので、 何も 10 kΩ にこだわる必要はありません。 10 kΩ を上回らない、 数 kΩ程度の値なら何でも結構です。

回路図では、マイコンのポートから配線が分岐して LCD とスイッチとに接続される形で 書かれていますが、実際は、(マイコン) - (LCD) - (抵抗) - (スイッチ) - (GND) と いうように、一筆書きで配線することができます。

タクト(プッシュ)スイッチは、ごく普通の、押して ON、放して OFF のタイプのものを使います。 また、簡易的ですが、(インクリメンタル)ロータリー・エンコーダをサポートしています。

使えるのは、デデント(引っかかり)があるタイプで、なおかつ、停止位置で A相、B相ともに オープンになるタイプです。 任意位相で停止したり、停止位置でオープンにならないタイプは、スイッチとの共存ができません。 その場合には、スイッチは使えず、ロータリー・エンコーダ専用になります。

マイコンと LCD は 4 ビットモードで接続していますから、 データ線は 4 本、つまり最大 4 個のスイッチを接続できます。 このうち、ひとつはシリアル MIDI モードのセンスに使っており、 残りの 3 本をキー入力スイッチに使っています。

少ない数のスイッチで多くの操作ができるように、キーの押し方により機能を変えています。 短く(約 0.5 秒以下)押すのを「クリック」(click)、長く(約 0.5 秒以上)押すのを 「長押し」(press)として認識します。

ロータリー・エンコーダのサポートは簡易的なもので、高速で回すと追従できません。 普通の速度で回すと「クリック」として認識されます。 右回転で「INC」、左回転で「DEC」です。 停止位置から次の停止位置まで、約 1 秒以上かけて、きわめてゆっくり回すと「長押し」と 認識されます。

「SHIFT」を押しながら他のキーを押すと、「クリック」と「長押し」の解釈を反対にします。 つまり、「SHIFT」を押しながら「クリック」すると「長押し」と解釈され、「SHIFT」を 押しながら「長押し」すると「クリック」と解釈されます。 「SHIFT」単独で押しても、何事も起こりません。

常に「クリック」と「長押し」を押し分けるのを前提とするなら、 「SHIFT」キーを実装する必要はありません。 ロータリー・エンコーダの場合は「SHIFT」キーを省略しないほうが良いでしょう。

「INC」長押しで「次の画面」、「DEC」長押しで「前の画面」、 「INC」クリックで「次の値」、「DEC」クリックで「前の値」の意味になります。 「画面」も「値」も循環していますから、増加させ続ける、または減少させ続けると、 いつかは元に戻ります。 したがって、面倒くさいのを我慢さえすれば、「INC」あるいは「DEC」の、 どちらか一方だけで用は足ります。

ATmega版の最小構成では、この考え方のもとに、「INC」スイッチだけを実装しています。 ADuC7026版の最小構成では、付録基板上の SW2 (リセットスイッチでない方)を 「INC」スイッチとして使います。 これは LCD のデータ線とは独立のポートを使っています。 もちろん、最大構成でも SW2 は有効です。

ソフトウェア的には、RAM 上に LCD 表示バッファ・メモリを設け、 バッファへのデータ書込み処理と、バッファからデータを読み出して LCD モジュールへ 出力する処理とを分離しています。 バッファ・メモリの内容にかかわらず、定期的にデータを読み出して LCD へ転送する処理が 常に動作しています。

CPU 負荷を少なくするために、LCD の「E」信号の周期は 2 ms に設定してあるので、 1文字の転送に 4 ms かかります。 したがって、LCD 表示内容をすべて「リフレッシュ」するためには、 2 * (16 + 1) * 4 [ms] = 136 [ms] を要します。 (16 + 1) の「+1」は、一行16文字分のデータ転送に先立って、 「DDRAM address set」コマンドを発行するためです。

一方、アプリケーション・プログラム側では、表示したい LCD 位置に対応する バッファ・メモリにデータを書き込むだけです。 そのデータが LCD に転送されるまで待つことはありません。 当然、リフレッシュ・レートより短い間隔でバッファ中のデータを書き換えても、 LCD 表示には反映されません。

● CPU 負荷メーター

ADuC7026 付録基板、V850ES/JG2 付録基板ともに、 基板上にポートに接続された LED が搭載されています。 プログラミングの手始めとして、この LED を利用して「LED チカチカ」プログラムを 実行させるのが、通例となっています。 どちらの基板でも、ポートに「L」レベルを出力すると LED が点灯します。

この LED を利用して、CPU 負荷を視覚的に表示できるようにしました。 処理の始めでポートに「H」を出力し LED を消灯します。 そして処理が終わるとポートに「L」を出力して、LED を点灯します。 MIDI データの到着待ちや、波形出力バッファが空くのを待っている状態、 つまり CPU のアイドル状態では LED を点灯したままにしておきます。

したがって、CPU が暇なら LED は明るく、CPU が忙しければ忙しいほど、LED は暗くなります。 CPU の処理中はポートに「H」が出力されているわけですから、 ポート出力は CPU の「ビジー」加減を、パルス幅変調(PWM)で表現していることになります。

デューティー測定ができるディジタルテスターで、このポートを測定すれば、CPU 負荷が 数値で表示されることになります。 同様のことをマイコンだけで実現するために、最大構成の回路図に示すように、PWM 波を 簡単な RC ローパスフィルタで平滑し、その電圧を内蔵の AD コンバータで測定しています。

平滑用のコンデンサと AD 入力の間の抵抗は重要です。 電源 OFF 時にコンデンサのチャージが AD 入力端子を通じて放電されるので、 もし AD 入力とコンデンサを直結すると過大な電流が流れます。 抵抗を挿入して電流を制限しています。

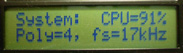

「システム設定/CPU負荷表示」の LCD 画面で、CPU 負荷をパーセント単位で表示できます。

測定精度に注意を払っていないので、目安程度に考えてください。

表示のための 10 進変換の都合で、表示の最大値は「99」で、決して「100」にはなりません。

「システム設定/CPU負荷表示」の LCD 画面で、CPU 負荷をパーセント単位で表示できます。

測定精度に注意を払っていないので、目安程度に考えてください。

表示のための 10 進変換の都合で、表示の最大値は「99」で、決して「100」にはなりません。